随着摩尔定律的发展,芯片的功能越来越强大,集成度也越来越高。然而随着10nm技术节点的接近,普通TFT面临着严重短沟道效应和高成本投入的双重严峻挑战。而肖特基势垒TFT由于具有低饱和电压、高本征增益、良好的环境稳定性、显著减弱的短沟道效应以及能够实现低功耗等特征优势而在近年来受到广泛研究和关注。相比于普通TFT,肖特基势垒TFT由于具有低饱和电压、高本征增益、良好的环境稳定性、显著减弱的短沟道效应以及能够实现低功耗等特征优势而在近年来受到广泛研究和关注。为实现源漏电极与IGZO沟道层间形成肖特基接触,过往许多研究一般是对电极和IGZO沟道层的界面进行氧等离子、反应溅射等处理,增加了制备工艺的复杂度,导致器件电学特性的严重衰退。

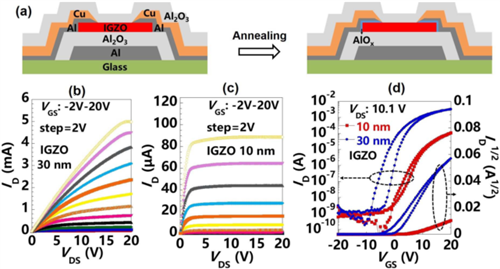

为了解决该问题,半导体所新型显示团队的研究人员采用Cu/Al叠层金属作为IGZO TFT的源漏电极,通过退火工艺使Al电极与IGZO接触部分自发氧化生成一层极薄的AlOx薄膜(~3nm),从而形成Cu/AlOx/IGZO肖特基异质结。一系列的研究证明,基于Cu源漏电极和AlOx插层制备的IGZO TFT表现出典型的肖特基接触特性,证实了该肖特基异质结的存在(如图1所示)。

图1 基于Cu/Al叠层电极的IGZO TFT结构示意图及其电学性能

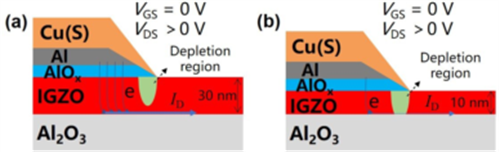

研究发现,通过调控沟道层的厚度可实现Cu/AlOx/IGZO肖特基异质结区与栅介质的接触界面,从而实现该肖特基TFT电学特性的大幅调控(如图2所示)。IGZO沟道层厚度为10nm时,器件表现出典型的肖特基势垒TFT特征,具有低至2.3V的饱和电压(VDS:0-20V)和高达80μA(VGS=20V)的输出电流;IGZO沟道层厚度为30 nm时,器件的输出特性表现出类似欧姆接触TFT特征,器件表观场效应迁移率高达82.9cm2/Vs。研究表明,Al/AlOx/IGZO异质结为欧姆接触结,具有显著小于Cu/AlOx/IGZO肖特基异质结的接触电阻,提高了电子注入IGZO沟道层的能力。该工作采用与显示工业相似的材料与工艺实现肖特基势垒IGZO TFT制备,对于促进肖特基势垒IGZO TFT的产业化应用具有借鉴意义。

图2 基于Cu/Al叠层源漏电极IGZO薄膜晶体管工作机理示意图

该工作得到了国家重点研发计划、省重点研发计划、中国博士后科学基金、及广东省科学院打造综合产业技术创新中心行动资金等项目资助,相关成果发表在期刊《IEEE Electron Device Letters》。省科学院半导体所新型显示团队成员胡诗犇博士为论文第一作者,李育智博士和龚政博士为共同通讯作者。

(供稿:新型显示团队)